Ethernet MAC module registers. More...

|

Functions | |

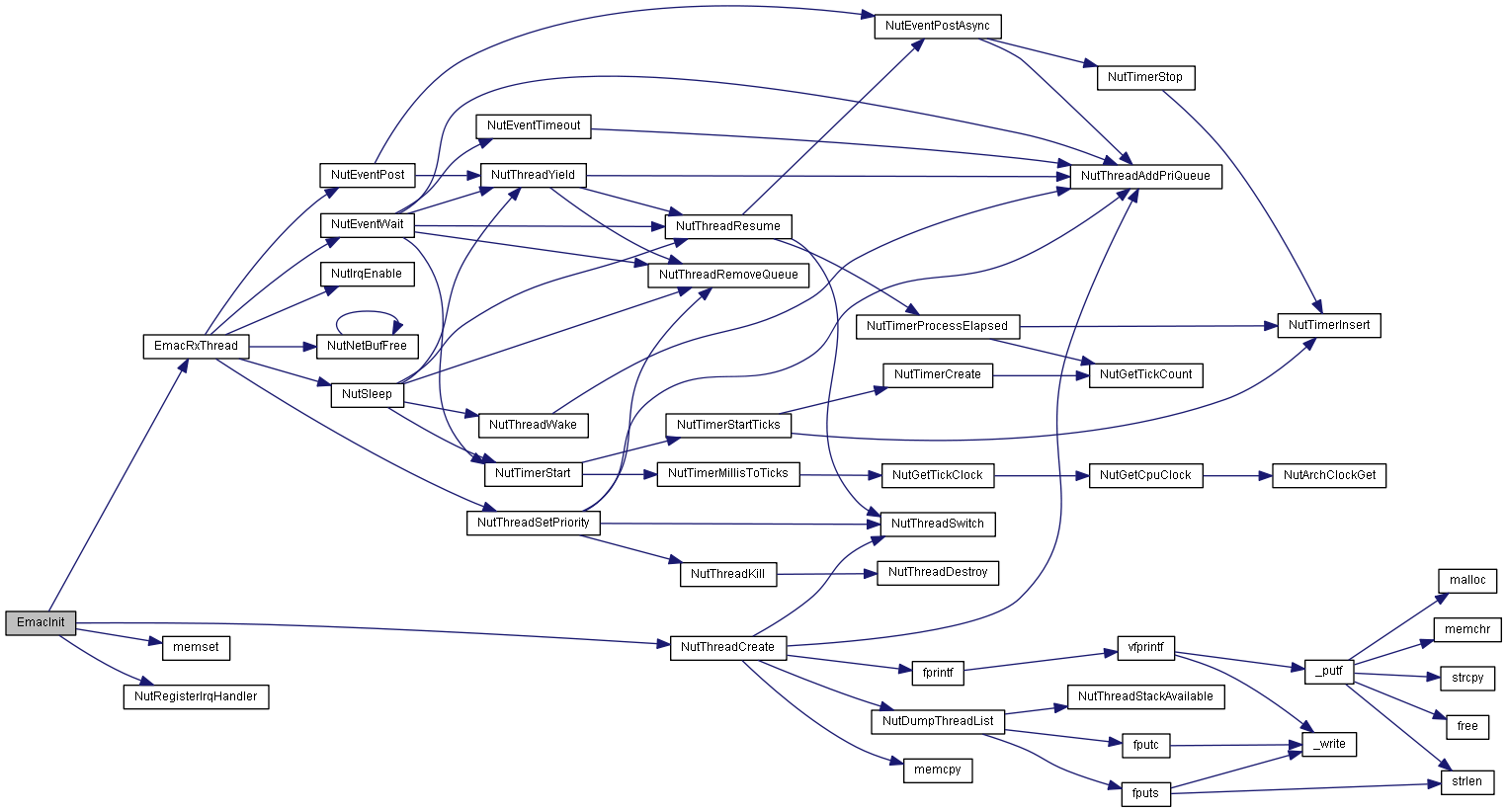

| void | EmacRxThread (void *arg) |

| NIC receiver thread. | |

| int | EmacOutput (NUTDEVICE *dev, NETBUF *nb) |

| Send Ethernet packet. | |

| int | EmacInit (NUTDEVICE *dev) |

| Initialize Ethernet hardware. | |

Variables | |

| NUTDEVICE | devAt91Emac |

| Device information structure. | |

| NUTDEVICE | devAvr32macb |

| Device information structure. | |

Network Control Register | |

| #define | EMAC_NCR_OFF 0x00000000 |

| Network control register offset. | |

| #define | EMAC_NCR (EMAC_BASE + EMAC_NCR_OFF) |

| Network Control register address. | |

| #define | EMAC_LB 0x00000001 |

| PHY loopback. | |

| #define | EMAC_LLB 0x00000002 |

| EMAC loopback. | |

| #define | EMAC_RE 0x00000004 |

| Receive enable. | |

| #define | EMAC_TE 0x00000008 |

| Transmit enable. | |

| #define | EMAC_MPE 0x00000010 |

| Management port enable. | |

| #define | EMAC_CLRSTAT 0x00000020 |

| Clear statistics registers. | |

| #define | EMAC_INCSTAT 0x00000040 |

| Increment statistics registers. | |

| #define | EMAC_WESTAT 0x00000080 |

| Write enable for statistics registers. | |

| #define | EMAC_BP 0x00000100 |

| Back pressure. | |

| #define | EMAC_TSTART 0x00000200 |

| Start Transmission. | |

| #define | EMAC_THALT 0x00000400 |

| Transmission halt. | |

| #define | EMAC_TPFR 0x00000800 |

| Transmit pause frame. | |

| #define | EMAC_TZQ 0x00001000 |

| Transmit zero quantum pause frame. | |

Network Configuration Register | |

| #define | EMAC_NCFGR_OFF 0x00000004 |

| Network configuration register offset. | |

| #define | EMAC_NCFGR (EMAC_BASE + EMAC_NCFGR_OFF) |

| Network configuration register address. | |

| #define | EMAC_SPD 0x00000001 |

| Speed, set for 100Mb. | |

| #define | EMAC_FD 0x00000002 |

| Full duplex. | |

| #define | EMAC_JFRAME 0x00000008 |

| Jumbo Frames. | |

| #define | EMAC_CAF 0x00000010 |

| Copy all frames. | |

| #define | EMAC_NBC 0x00000020 |

| No broadcast. | |

| #define | EMAC_MTI 0x00000040 |

| Multicast hash event enable. | |

| #define | EMAC_UNI 0x00000080 |

| Unicast hash enable. | |

| #define | EMAC_BIG 0x00000100 |

| Receive 1522 bytes. | |

| #define | EMAC_EAE 0x00000200 |

| External address match enable. | |

| #define | EMAC_CLK 0x00000C00 |

| Clock divider mask. | |

| #define | EMAC_CLK_HCLK_8 0x00000000 |

| HCLK divided by 8. | |

| #define | EMAC_CLK_HCLK_16 0x00000400 |

| HCLK divided by 16. | |

| #define | EMAC_CLK_HCLK_32 0x00000800 |

| HCLK divided by 32. | |

| #define | EMAC_CLK_HCLK_64 0x00000C00 |

| HCLK divided by 64. | |

| #define | EMAC_RTY 0x00001000 |

| Retry test. | |

| #define | EMAC_PAE 0x00002000 |

| Pause enable. | |

| #define | EMAC_RBOF 0x0000C000 |

| Receive buffer offset. | |

| #define | EMAC_RBOF_OFFSET_0 0x00000000 |

| No offset from start of receive buffer. | |

| #define | EMAC_RBOF_OFFSET_1 0x00004000 |

| One byte offset from start of receive buffer. | |

| #define | EMAC_RBOF_OFFSET_2 0x00008000 |

| Two bytes offset from start of receive buffer. | |

| #define | EMAC_RBOF_OFFSET_3 0x0000C000 |

| Three bytes offset from start of receive buffer. | |

| #define | EMAC_RLCE 0x00010000 |

| Receive length field checking enable. | |

| #define | EMAC_DRFCS 0x00020000 |

| Discard receive FCS. | |

| #define | EMAC_EFRHD 0x00040000 |

| Allow receive during transmit in half duplex. | |

| #define | EMAC_IRXFCS 0x00080000 |

| Ignore received FCS. | |

Network Status Register | |

| #define | EMAC_NSR_OFF 0x00000008 |

| Network Status register offset. | |

| #define | EMAC_NSR (EMAC_BASE + EMAC_NSR_OFF) |

| Network Status register address. | |

| #define | EMAC_LINKR 0x00000001 |

| | |

| #define | EMAC_MDIO 0x00000002 |

| Status of MDIO input pin. | |

| #define | EMAC_IDLE 0x00000004 |

| Set when PHY is running. | |

Transmit Status Register | |

| #define | EMAC_TSR_OFF 0x00000014 |

| Transmit Status register offset. | |

| #define | EMAC_TSR (EMAC_BASE + EMAC_TSR_OFF) |

| Transmit Status register address. | |

| #define | EMAC_UBR 0x00000001 |

| Used bit read. | |

| #define | EMAC_COL 0x00000002 |

| Collision occurred. | |

| #define | EMAC_RLES 0x00000004 |

| Retry limit exceeded. | |

| #define | EMAC_TGO 0x00000008 |

| Transmit active. | |

| #define | EMAC_BEX 0x00000010 |

| Buffers exhausted mid frame. | |

| #define | EMAC_COMP 0x00000020 |

| Transmit complete. | |

| #define | EMAC_UND 0x00000040 |

| Transmit underrun. | |

Buffer Queue Pointer Register | |

| #define | EMAC_RBQP_OFF 0x00000018 |

| Receive buffer queue pointer. | |

| #define | EMAC_RBQP (EMAC_BASE + EMAC_RBQP_OFF) |

| Receive buffer queue pointer. | |

| #define | EMAC_TBQP_OFF 0x0000001C |

| Transmit buffer queue pointer. | |

| #define | EMAC_TBQP (EMAC_BASE + EMAC_TBQP_OFF) |

| Transmit buffer queue pointer. | |

Receive Status Register | |

| #define | EMAC_RSR_OFF 0x00000020 |

| Receive status register offset. | |

| #define | EMAC_RSR (EMAC_BASE + EMAC_RSR_OFF) |

| Receive status register address. | |

| #define | EMAC_BNA 0x00000001 |

| Buffer not available. | |

| #define | EMAC_REC 0x00000002 |

| Frame received. | |

| #define | EMAC_OVR 0x00000004 |

| Receive overrun. | |

Interrupt Registers | |

| #define | EMAC_ISR_OFF 0x00000024 |

| Status register offset. | |

| #define | EMAC_ISR (EMAC_BASE + EMAC_ISR_OFF) |

| Status register address. | |

| #define | EMAC_IER_OFF 0x00000028 |

| Enable register offset. | |

| #define | EMAC_IER (EMAC_BASE + EMAC_IER_OFF) |

| Enable register address. | |

| #define | EMAC_IDR_OFF 0x0000002C |

| Disable register offset. | |

| #define | EMAC_IDR (EMAC_BASE + EMAC_IDR_OFF) |

| Disable register address. | |

| #define | EMAC_IMR_OFF 0x00000030 |

| Mask register offset. | |

| #define | EMAC_IMR (EMAC_BASE + EMAC_IMR_OFF) |

| Mask register address. | |

| #define | EMAC_MFD 0x00000001 |

| Management frame done. | |

| #define | EMAC_RCOMP 0x00000002 |

| Receive complete. | |

| #define | EMAC_RXUBR 0x00000004 |

| Receive used bit read. | |

| #define | EMAC_TXUBR 0x00000008 |

| Transmit used bit read. | |

| #define | EMAC_TUND 0x00000010 |

| Ethernet transmit buffer underrun. | |

| #define | EMAC_RLEX 0x00000020 |

| Retry limit exceeded. | |

| #define | EMAC_TXERR 0x00000040 |

| Transmit error. | |

| #define | EMAC_TCOMP 0x00000080 |

| Transmit complete. | |

| #define | EMAC_LINK 0x00000200 |

| | |

| #define | EMAC_ROVR 0x00000400 |

| Receive overrun. | |

| #define | EMAC_HRESP 0x00000800 |

| DMA bus error. | |

| #define | EMAC_PFR 0x00001000 |

| Pause frame received. | |

| #define | EMAC_PTZ 0x00002000 |

| Pause time zero. | |

PHY Maintenance Register | |

| #define | EMAC_MAN_OFF 0x00000034 |

| PHY maintenance register offset. | |

| #define | EMAC_MAN (EMAC_BASE + EMAC_MAN_OFF) |

| PHY maintenance register address. | |

| #define | EMAC_DATA 0x0000FFFF |

| PHY data mask. | |

| #define | EMAC_DATA_LSB 0 |

| PHY data LSB. | |

| #define | EMAC_CODE 0x00020000 |

| Fixed value. | |

| #define | EMAC_REGA 0x007C0000 |

| PHY register address mask. | |

| #define | EMAC_REGA_LSB 18 |

| PHY register address LSB. | |

| #define | EMAC_PHYA 0x0F800000 |

| PHY address mask. | |

| #define | EMAC_PHYA_LSB 23 |

| PHY address LSB. | |

| #define | EMAC_RW 0x30000000 |

| PHY read/write command mask. | |

| #define | EMAC_RW_READ 0x20000000 |

| PHY read command. | |

| #define | EMAC_RW_WRITE 0x10000000 |

| PHY write command. | |

| #define | EMAC_SOF 0x40000000 |

| Fixed value. | |

Pause Time Register | |

| #define | EMAC_PTR_OFF 0x00000038 |

| Pause time register offset. | |

| #define | EMAC_PTR (EMAC_BASE + EMAC_PTR_OFF) |

| Pause time register address. | |

| #define | EMAC_PTIME 0x0000FFFF |

| Pause time mask. | |

Statistics Registers | |

| #define | EMAC_PFRR_OFF 0x0000003C |

| Pause frames received register offset. | |

| #define | EMAC_PFRR (EMAC_BASE + EMAC_PFRR_OFF) |

| Pause frames received register address. | |

| #define | EMAC_FTO_OFF 0x00000040 |

| Frames transmitted OK register offset. | |

| #define | EMAC_FTO (EMAC_BASE + EMAC_FTO_OFF) |

| Frames transmitted OK register address. | |

| #define | EMAC_SCF_OFF 0x00000044 |

| Single collision frame register offset. | |

| #define | EMAC_SCF (EMAC_BASE + EMAC_SCF_OFF) |

| Single collision frame register address. | |

| #define | EMAC_MCF_OFF 0x00000048 |

| Multiple collision frame register offset. | |

| #define | EMAC_MCF (EMAC_BASE + EMAC_MCF_OFF) |

| Multiple collision frame register address. | |

| #define | EMAC_FRO_OFF 0x0000004C |

| Frames received OK register offset. | |

| #define | EMAC_FRO (EMAC_BASE + EMAC_FRO_OFF) |

| Frames received OK register address. | |

| #define | EMAC_FCSE_OFF 0x00000050 |

| Frame check sequence error register offset. | |

| #define | EMAC_FCSE (EMAC_BASE + EMAC_FCSE_OFF) |

| Frame check sequence error register address. | |

| #define | EMAC_ALE_OFF 0x00000054 |

| Alignment error register offset. | |

| #define | EMAC_ALE (EMAC_BASE + EMAC_ALE_OFF) |

| Alignment error register address. | |

| #define | EMAC_DTF_OFF 0x00000058 |

| Deferred transmission frame register offset. | |

| #define | EMAC_DTF (EMAC_BASE + EMAC_DTF_OFF) |

| Deferred transmission frame register address. | |

| #define | EMAC_LCOL_OFF 0x0000005C |

| Late collision register offset. | |

| #define | EMAC_LCOL (EMAC_BASE + EMAC_LCOL_OFF) |

| Late collision register address. | |

| #define | EMAC_ECOL_OFF 0x00000060 |

| Excessive collision register offset. | |

| #define | EMAC_ECOL (EMAC_BASE + EMAC_ECOL_OFF) |

| Excessive collision register address. | |

| #define | EMAC_TUNDR_OFF 0x00000064 |

| Transmit underrun error register offset. | |

| #define | EMAC_TUNDR (EMAC_BASE + EMAC_TUNDR_OFF) |

| Transmit underrun error register address. | |

| #define | EMAC_CSE_OFF 0x00000068 |

| Carrier sense error register offset. | |

| #define | EMAC_CSE (EMAC_BASE + EMAC_CSE_OFF) |

| Carrier sense error register address. | |

| #define | EMAC_RRE_OFF 0x0000006C |

| Receive resource error register offset. | |

| #define | EMAC_RRE (EMAC_BASE + EMAC_RRE_OFF) |

| Receive resource error register address. | |

| #define | EMAC_ROV_OFF 0x00000070 |

| Receive overrun errors register offset. | |

| #define | EMAC_ROV (EMAC_BASE + EMAC_ROV_OFF) |

| Receive overrun errors register address. | |

| #define | EMAC_RSE_OFF 0x00000074 |

| Receive symbol errors register offset. | |

| #define | EMAC_RSE (EMAC_BASE + EMAC_RSE_OFF) |

| Receive symbol errors register address. | |

| #define | EMAC_ELE_OFF 0x00000078 |

| Excessive length errors register offset. | |

| #define | EMAC_ELE (EMAC_BASE + EMAC_ELE_OFF) |

| Excessive length errors register address. | |

| #define | EMAC_RJA_OFF 0x0000007C |

| Receive jabbers register offset. | |

| #define | EMAC_RJA (EMAC_BASE + EMAC_RJA_OFF) |

| Receive jabbers register address. | |

| #define | EMAC_USF_OFF 0x00000080 |

| Undersize frames register offset. | |

| #define | EMAC_USF (EMAC_BASE + EMAC_USF_OFF) |

| Undersize frames register address. | |

| #define | EMAC_STE_OFF 0x00000084 |

| SQE test error register offset. | |

| #define | EMAC_STE (EMAC_BASE + EMAC_STE_OFF) |

| SQE test error register address. | |

| #define | EMAC_RLE_OFF 0x00000088 |

| Receive length field mismatch register offset. | |

| #define | EMAC_RLE (EMAC_BASE + EMAC_RLE_OFF) |

| Receive length field mismatch register address. | |

| #define | EMAC_TPF_OFF 0x0000008C |

| Transmitted pause frames register offset. | |

| #define | EMAC_TPF (EMAC_BASE + EMAC_TPF_OFF) |

| Transmitted pause frames register address. | |

MAC Adressing Registers | |

| #define | EMAC_HRB_OFF 0x00000090 |

| Hash address bottom[31:0]. | |

| #define | EMAC_HRB (EMAC_BASE + EMAC_HRB_OFF) |

| Hash address bottom[31:0]. | |

| #define | EMAC_HRT_OFF 0x00000094 |

| Hash address top[63:32]. | |

| #define | EMAC_HRT (EMAC_BASE + EMAC_HRT_OFF) |

| Hash address top[63:32]. | |

| #define | EMAC_SA1L_OFF 0x00000098 |

| Specific address 1 bottom, first 4 bytes. | |

| #define | EMAC_SA1L (EMAC_BASE + EMAC_SA1L_OFF) |

| Specific address 1 bottom, first 4 bytes. | |

| #define | EMAC_SA1H_OFF 0x0000009C |

| Specific address 1 top, last 2 bytes. | |

| #define | EMAC_SA1H (EMAC_BASE + EMAC_SA1H_OFF) |

| Specific address 1 top, last 2 bytes. | |

| #define | EMAC_SA2L_OFF 0x000000A0 |

| Specific address 2 bottom, first 4 bytes. | |

| #define | EMAC_SA2L (EMAC_BASE + EMAC_SA2L_OFF) |

| Specific address 2 bottom, first 4 bytes. | |

| #define | EMAC_SA2H_OFF 0x000000A4 |

| Specific address 2 top, last 2 bytes. | |

| #define | EMAC_SA2H (EMAC_BASE + EMAC_SA2H_OFF) |

| Specific address 2 top, last 2 bytes. | |

| #define | EMAC_SA3L_OFF 0x000000A8 |

| Specific address 3 bottom, first 4 bytes. | |

| #define | EMAC_SA3L (EMAC_BASE + EMAC_SA3L_OFF) |

| Specific address 3 bottom, first 4 bytes. | |

| #define | EMAC_SA3H_OFF 0x000000AC |

| Specific address 3 top, last 2 bytes. | |

| #define | EMAC_SA3H (EMAC_BASE + EMAC_SA3H_OFF) |

| Specific address 3 top, last 2 bytes. | |

| #define | EMAC_SA4L_OFF 0x000000B0 |

| Specific address 4 bottom, first 4 bytes. | |

| #define | EMAC_SA4L (EMAC_BASE + EMAC_SA4L_OFF) |

| Specific address 4 bottom, first 4 bytes. | |

| #define | EMAC_SA4H_OFF 0x000000B4 |

| Specific address 4 top, last 2 bytes. | |

| #define | EMAC_SA4H (EMAC_BASE + EMAC_SA4H_OFF) |

| Specific address 4 top, last 2 bytes. | |

Type ID Register | |

| #define | EMAC_TID_OFF 0x000000B8 |

| Type ID checking register offset. | |

| #define | EMAC_TID (EMAC_BASE + EMAC_TID_OFF) |

| Type ID checking register address. | |

| #define | EMAC_TPQ_OFF 0x000000BC |

| Transmit pause quantum register offset. | |

| #define | EMAC_TPQ (EMAC_BASE + EMAC_TPQ_OFF) |

| Transmit pause quantum register address. | |

User Input/Output Register | |

| #define | EMAC_USRIO_OFF 0x000000C0 |

| User input/output register offset. | |

| #define | EMAC_USRIO (EMAC_BASE + EMAC_USRIO_OFF) |

| User input/output register address. | |

| #define | EMAC_RMII 0x00000001 |

| Enable reduced MII. | |

| #define | EMAC_CLKEN 0x00000002 |

| Enable tranceiver input clock. | |

Wake On LAN Register | |

| #define | EMAC_WOL_OFF 0x000000C4 |

| Wake On LAN register offset. | |

| #define | EMAC_WOL (EMAC_BASE + EMAC_WOL_OFF) |

| Wake On LAN register address. | |

| #define | EMAC_IP 0x0000FFFF |

| ARP request IP address mask. | |

| #define | EMAC_MAG 0x00010000 |

| Magic packet event enable. | |

| #define | EMAC_ARP 0x00020000 |

| ARP request event enable. | |

| #define | EMAC_SA1 0x00040000 |

| Specific address register 1 event enable. | |

Revision Register | |

| #define | EMAC_REV_OFF 0x000000FC |

| Revision register offset. | |

| #define | EMAC_REV (EMAC_BASE + EMAC_REV_OFF) |

| Revision register address. | |

| #define | EMAC_REVREF 0x0000FFFF |

| Revision. | |

| #define | EMAC_PARTREF 0xFFFF0000 |

| Part. | |

Ethernet MAC module registers.

| #define EMAC_NCR_OFF 0x00000000 |

Network control register offset.

Definition at line 59 of file at91_emac.h.

| #define EMAC_NCR (EMAC_BASE + EMAC_NCR_OFF) |

Network Control register address.

Definition at line 60 of file at91_emac.h.

| #define EMAC_LB 0x00000001 |

PHY loopback.

Definition at line 62 of file at91_emac.h.

| #define EMAC_LLB 0x00000002 |

EMAC loopback.

Definition at line 63 of file at91_emac.h.

| #define EMAC_RE 0x00000004 |

Receive enable.

Definition at line 64 of file at91_emac.h.

| #define EMAC_TE 0x00000008 |

Transmit enable.

Definition at line 65 of file at91_emac.h.

| #define EMAC_MPE 0x00000010 |

Management port enable.

Definition at line 66 of file at91_emac.h.

| #define EMAC_CLRSTAT 0x00000020 |

Clear statistics registers.

Definition at line 67 of file at91_emac.h.

| #define EMAC_INCSTAT 0x00000040 |

Increment statistics registers.

Definition at line 68 of file at91_emac.h.

| #define EMAC_WESTAT 0x00000080 |

Write enable for statistics registers.

Definition at line 69 of file at91_emac.h.

| #define EMAC_BP 0x00000100 |

Back pressure.

Definition at line 70 of file at91_emac.h.

| #define EMAC_TSTART 0x00000200 |

Start Transmission.

Definition at line 71 of file at91_emac.h.

| #define EMAC_THALT 0x00000400 |

Transmission halt.

Definition at line 72 of file at91_emac.h.

| #define EMAC_TPFR 0x00000800 |

Transmit pause frame.

Definition at line 73 of file at91_emac.h.

| #define EMAC_TZQ 0x00001000 |

Transmit zero quantum pause frame.

Definition at line 74 of file at91_emac.h.

| #define EMAC_NCFGR_OFF 0x00000004 |

Network configuration register offset.

Definition at line 79 of file at91_emac.h.

| #define EMAC_NCFGR (EMAC_BASE + EMAC_NCFGR_OFF) |

Network configuration register address.

Definition at line 80 of file at91_emac.h.

| #define EMAC_SPD 0x00000001 |

Speed, set for 100Mb.

Definition at line 82 of file at91_emac.h.

| #define EMAC_FD 0x00000002 |

Full duplex.

Definition at line 83 of file at91_emac.h.

| #define EMAC_JFRAME 0x00000008 |

Jumbo Frames.

Definition at line 84 of file at91_emac.h.

| #define EMAC_CAF 0x00000010 |

Copy all frames.

Definition at line 85 of file at91_emac.h.

| #define EMAC_NBC 0x00000020 |

No broadcast.

Definition at line 86 of file at91_emac.h.

| #define EMAC_MTI 0x00000040 |

Multicast hash event enable.

Definition at line 87 of file at91_emac.h.

| #define EMAC_UNI 0x00000080 |

Unicast hash enable.

Definition at line 88 of file at91_emac.h.

| #define EMAC_BIG 0x00000100 |

Receive 1522 bytes.

Definition at line 89 of file at91_emac.h.

| #define EMAC_EAE 0x00000200 |

External address match enable.

Definition at line 90 of file at91_emac.h.

| #define EMAC_CLK 0x00000C00 |

Clock divider mask.

Definition at line 91 of file at91_emac.h.

| #define EMAC_CLK_HCLK_8 0x00000000 |

HCLK divided by 8.

Definition at line 92 of file at91_emac.h.

| #define EMAC_CLK_HCLK_16 0x00000400 |

HCLK divided by 16.

Definition at line 93 of file at91_emac.h.

| #define EMAC_CLK_HCLK_32 0x00000800 |

HCLK divided by 32.

Definition at line 94 of file at91_emac.h.

| #define EMAC_CLK_HCLK_64 0x00000C00 |

HCLK divided by 64.

Definition at line 95 of file at91_emac.h.

| #define EMAC_RTY 0x00001000 |

Retry test.

Definition at line 96 of file at91_emac.h.

| #define EMAC_PAE 0x00002000 |

Pause enable.

Definition at line 97 of file at91_emac.h.

| #define EMAC_RBOF 0x0000C000 |

Receive buffer offset.

Definition at line 98 of file at91_emac.h.

| #define EMAC_RBOF_OFFSET_0 0x00000000 |

No offset from start of receive buffer.

Definition at line 99 of file at91_emac.h.

| #define EMAC_RBOF_OFFSET_1 0x00004000 |

One byte offset from start of receive buffer.

Definition at line 100 of file at91_emac.h.

| #define EMAC_RBOF_OFFSET_2 0x00008000 |

Two bytes offset from start of receive buffer.

Definition at line 101 of file at91_emac.h.

| #define EMAC_RBOF_OFFSET_3 0x0000C000 |

Three bytes offset from start of receive buffer.

Definition at line 102 of file at91_emac.h.

| #define EMAC_RLCE 0x00010000 |

Receive length field checking enable.

Definition at line 103 of file at91_emac.h.

| #define EMAC_DRFCS 0x00020000 |

Discard receive FCS.

Definition at line 104 of file at91_emac.h.

| #define EMAC_EFRHD 0x00040000 |

Allow receive during transmit in half duplex.

Definition at line 105 of file at91_emac.h.

| #define EMAC_IRXFCS 0x00080000 |

Ignore received FCS.

Definition at line 106 of file at91_emac.h.

| #define EMAC_NSR_OFF 0x00000008 |

Network Status register offset.

Definition at line 111 of file at91_emac.h.

| #define EMAC_NSR (EMAC_BASE + EMAC_NSR_OFF) |

Network Status register address.

Definition at line 112 of file at91_emac.h.

| #define EMAC_LINKR 0x00000001 |

Definition at line 113 of file at91_emac.h.

| #define EMAC_MDIO 0x00000002 |

Status of MDIO input pin.

Definition at line 114 of file at91_emac.h.

| #define EMAC_IDLE 0x00000004 |

Set when PHY is running.

Definition at line 115 of file at91_emac.h.

| #define EMAC_TSR_OFF 0x00000014 |

Transmit Status register offset.

Definition at line 120 of file at91_emac.h.

| #define EMAC_TSR (EMAC_BASE + EMAC_TSR_OFF) |

Transmit Status register address.

Definition at line 121 of file at91_emac.h.

Referenced by EmacOutput().

| #define EMAC_UBR 0x00000001 |

Used bit read.

Definition at line 123 of file at91_emac.h.

| #define EMAC_COL 0x00000002 |

Collision occurred.

Definition at line 124 of file at91_emac.h.

| #define EMAC_RLES 0x00000004 |

Retry limit exceeded.

Definition at line 125 of file at91_emac.h.

| #define EMAC_TGO 0x00000008 |

Transmit active.

Definition at line 126 of file at91_emac.h.

| #define EMAC_BEX 0x00000010 |

Buffers exhausted mid frame.

Definition at line 127 of file at91_emac.h.

| #define EMAC_COMP 0x00000020 |

| #define EMAC_UND 0x00000040 |

| #define EMAC_RBQP_OFF 0x00000018 |

Receive buffer queue pointer.

Definition at line 134 of file at91_emac.h.

| #define EMAC_RBQP (EMAC_BASE + EMAC_RBQP_OFF) |

Receive buffer queue pointer.

Definition at line 135 of file at91_emac.h.

| #define EMAC_TBQP_OFF 0x0000001C |

Transmit buffer queue pointer.

Definition at line 136 of file at91_emac.h.

| #define EMAC_TBQP (EMAC_BASE + EMAC_TBQP_OFF) |

Transmit buffer queue pointer.

Definition at line 137 of file at91_emac.h.

| #define EMAC_RSR_OFF 0x00000020 |

Receive status register offset.

Definition at line 142 of file at91_emac.h.

| #define EMAC_RSR (EMAC_BASE + EMAC_RSR_OFF) |

Receive status register address.

Definition at line 143 of file at91_emac.h.

| #define EMAC_BNA 0x00000001 |

Buffer not available.

Definition at line 145 of file at91_emac.h.

| #define EMAC_REC 0x00000002 |

Frame received.

Definition at line 146 of file at91_emac.h.

| #define EMAC_OVR 0x00000004 |

Receive overrun.

Definition at line 147 of file at91_emac.h.

| #define EMAC_ISR_OFF 0x00000024 |

Status register offset.

Definition at line 152 of file at91_emac.h.

| #define EMAC_ISR (EMAC_BASE + EMAC_ISR_OFF) |

Status register address.

Definition at line 153 of file at91_emac.h.

| #define EMAC_IER_OFF 0x00000028 |

Enable register offset.

Definition at line 154 of file at91_emac.h.

| #define EMAC_IER (EMAC_BASE + EMAC_IER_OFF) |

| #define EMAC_IDR_OFF 0x0000002C |

Disable register offset.

Definition at line 156 of file at91_emac.h.

| #define EMAC_IDR (EMAC_BASE + EMAC_IDR_OFF) |

Disable register address.

Definition at line 157 of file at91_emac.h.

| #define EMAC_IMR_OFF 0x00000030 |

Mask register offset.

Definition at line 158 of file at91_emac.h.

| #define EMAC_IMR (EMAC_BASE + EMAC_IMR_OFF) |

Mask register address.

Definition at line 159 of file at91_emac.h.

| #define EMAC_MFD 0x00000001 |

Management frame done.

Definition at line 161 of file at91_emac.h.

| #define EMAC_RCOMP 0x00000002 |

| #define EMAC_RXUBR 0x00000004 |

| #define EMAC_TXUBR 0x00000008 |

Transmit used bit read.

Definition at line 164 of file at91_emac.h.

| #define EMAC_TUND 0x00000010 |

Ethernet transmit buffer underrun.

Definition at line 165 of file at91_emac.h.

Referenced by EmacRxThread().

| #define EMAC_RLEX 0x00000020 |

Retry limit exceeded.

Definition at line 166 of file at91_emac.h.

| #define EMAC_TXERR 0x00000040 |

Transmit error.

Definition at line 167 of file at91_emac.h.

| #define EMAC_TCOMP 0x00000080 |

Transmit complete.

Definition at line 168 of file at91_emac.h.

| #define EMAC_LINK 0x00000200 |

Definition at line 169 of file at91_emac.h.

| #define EMAC_ROVR 0x00000400 |

| #define EMAC_HRESP 0x00000800 |

DMA bus error.

Definition at line 171 of file at91_emac.h.

| #define EMAC_PFR 0x00001000 |

Pause frame received.

Definition at line 172 of file at91_emac.h.

| #define EMAC_PTZ 0x00002000 |

Pause time zero.

Definition at line 173 of file at91_emac.h.

| #define EMAC_MAN_OFF 0x00000034 |

PHY maintenance register offset.

Definition at line 178 of file at91_emac.h.

| #define EMAC_MAN (EMAC_BASE + EMAC_MAN_OFF) |

PHY maintenance register address.

Definition at line 179 of file at91_emac.h.

| #define EMAC_DATA 0x0000FFFF |

PHY data mask.

Definition at line 181 of file at91_emac.h.

| #define EMAC_DATA_LSB 0 |

PHY data LSB.

Definition at line 182 of file at91_emac.h.

| #define EMAC_CODE 0x00020000 |

Fixed value.

Definition at line 183 of file at91_emac.h.

| #define EMAC_REGA 0x007C0000 |

PHY register address mask.

Definition at line 184 of file at91_emac.h.

| #define EMAC_REGA_LSB 18 |

PHY register address LSB.

Definition at line 185 of file at91_emac.h.

| #define EMAC_PHYA 0x0F800000 |

PHY address mask.

Definition at line 186 of file at91_emac.h.

| #define EMAC_PHYA_LSB 23 |

PHY address LSB.

Definition at line 187 of file at91_emac.h.

| #define EMAC_RW 0x30000000 |

PHY read/write command mask.

Definition at line 188 of file at91_emac.h.

| #define EMAC_RW_READ 0x20000000 |

PHY read command.

Definition at line 189 of file at91_emac.h.

| #define EMAC_RW_WRITE 0x10000000 |

PHY write command.

Definition at line 190 of file at91_emac.h.

| #define EMAC_SOF 0x40000000 |

Fixed value.

Definition at line 191 of file at91_emac.h.

| #define EMAC_PTR_OFF 0x00000038 |

Pause time register offset.

Definition at line 196 of file at91_emac.h.

| #define EMAC_PTR (EMAC_BASE + EMAC_PTR_OFF) |

Pause time register address.

Definition at line 197 of file at91_emac.h.

| #define EMAC_PTIME 0x0000FFFF |

Pause time mask.

Definition at line 199 of file at91_emac.h.

| #define EMAC_PFRR_OFF 0x0000003C |

Pause frames received register offset.

Definition at line 204 of file at91_emac.h.

| #define EMAC_PFRR (EMAC_BASE + EMAC_PFRR_OFF) |

Pause frames received register address.

Definition at line 205 of file at91_emac.h.

| #define EMAC_FTO_OFF 0x00000040 |

Frames transmitted OK register offset.

Definition at line 206 of file at91_emac.h.

| #define EMAC_FTO (EMAC_BASE + EMAC_FTO_OFF) |

Frames transmitted OK register address.

Definition at line 207 of file at91_emac.h.

| #define EMAC_SCF_OFF 0x00000044 |

Single collision frame register offset.

Definition at line 208 of file at91_emac.h.

| #define EMAC_SCF (EMAC_BASE + EMAC_SCF_OFF) |

Single collision frame register address.

Definition at line 209 of file at91_emac.h.

| #define EMAC_MCF_OFF 0x00000048 |

Multiple collision frame register offset.

Definition at line 210 of file at91_emac.h.

| #define EMAC_MCF (EMAC_BASE + EMAC_MCF_OFF) |

Multiple collision frame register address.

Definition at line 211 of file at91_emac.h.

| #define EMAC_FRO_OFF 0x0000004C |

Frames received OK register offset.

Definition at line 212 of file at91_emac.h.

| #define EMAC_FRO (EMAC_BASE + EMAC_FRO_OFF) |

Frames received OK register address.

Definition at line 213 of file at91_emac.h.

| #define EMAC_FCSE_OFF 0x00000050 |

Frame check sequence error register offset.

Definition at line 214 of file at91_emac.h.

| #define EMAC_FCSE (EMAC_BASE + EMAC_FCSE_OFF) |

Frame check sequence error register address.

Definition at line 215 of file at91_emac.h.

| #define EMAC_ALE_OFF 0x00000054 |

Alignment error register offset.

Definition at line 216 of file at91_emac.h.

| #define EMAC_ALE (EMAC_BASE + EMAC_ALE_OFF) |

Alignment error register address.

Definition at line 217 of file at91_emac.h.

| #define EMAC_DTF_OFF 0x00000058 |

Deferred transmission frame register offset.

Definition at line 218 of file at91_emac.h.

| #define EMAC_DTF (EMAC_BASE + EMAC_DTF_OFF) |

Deferred transmission frame register address.

Definition at line 219 of file at91_emac.h.

| #define EMAC_LCOL_OFF 0x0000005C |

Late collision register offset.

Definition at line 220 of file at91_emac.h.

| #define EMAC_LCOL (EMAC_BASE + EMAC_LCOL_OFF) |

Late collision register address.

Definition at line 221 of file at91_emac.h.

| #define EMAC_ECOL_OFF 0x00000060 |

Excessive collision register offset.

Definition at line 222 of file at91_emac.h.

| #define EMAC_ECOL (EMAC_BASE + EMAC_ECOL_OFF) |

Excessive collision register address.

Definition at line 223 of file at91_emac.h.

| #define EMAC_TUNDR_OFF 0x00000064 |

Transmit underrun error register offset.

Definition at line 224 of file at91_emac.h.

| #define EMAC_TUNDR (EMAC_BASE + EMAC_TUNDR_OFF) |

Transmit underrun error register address.

Definition at line 225 of file at91_emac.h.

| #define EMAC_CSE_OFF 0x00000068 |

Carrier sense error register offset.

Definition at line 226 of file at91_emac.h.

| #define EMAC_CSE (EMAC_BASE + EMAC_CSE_OFF) |

Carrier sense error register address.

Definition at line 227 of file at91_emac.h.

| #define EMAC_RRE_OFF 0x0000006C |

Receive resource error register offset.

Definition at line 228 of file at91_emac.h.

| #define EMAC_RRE (EMAC_BASE + EMAC_RRE_OFF) |

Receive resource error register address.

Definition at line 229 of file at91_emac.h.

| #define EMAC_ROV_OFF 0x00000070 |

Receive overrun errors register offset.

Definition at line 230 of file at91_emac.h.

| #define EMAC_ROV (EMAC_BASE + EMAC_ROV_OFF) |

Receive overrun errors register address.

Definition at line 231 of file at91_emac.h.

| #define EMAC_RSE_OFF 0x00000074 |

Receive symbol errors register offset.

Definition at line 232 of file at91_emac.h.

| #define EMAC_RSE (EMAC_BASE + EMAC_RSE_OFF) |

Receive symbol errors register address.

Definition at line 233 of file at91_emac.h.

| #define EMAC_ELE_OFF 0x00000078 |

Excessive length errors register offset.

Definition at line 234 of file at91_emac.h.

| #define EMAC_ELE (EMAC_BASE + EMAC_ELE_OFF) |

Excessive length errors register address.

Definition at line 235 of file at91_emac.h.

| #define EMAC_RJA_OFF 0x0000007C |

Receive jabbers register offset.

Definition at line 236 of file at91_emac.h.

| #define EMAC_RJA (EMAC_BASE + EMAC_RJA_OFF) |

Receive jabbers register address.

Definition at line 237 of file at91_emac.h.

| #define EMAC_USF_OFF 0x00000080 |

Undersize frames register offset.

Definition at line 238 of file at91_emac.h.

| #define EMAC_USF (EMAC_BASE + EMAC_USF_OFF) |

Undersize frames register address.

Definition at line 239 of file at91_emac.h.

| #define EMAC_STE_OFF 0x00000084 |

SQE test error register offset.

Definition at line 240 of file at91_emac.h.

| #define EMAC_STE (EMAC_BASE + EMAC_STE_OFF) |

SQE test error register address.

Definition at line 241 of file at91_emac.h.

| #define EMAC_RLE_OFF 0x00000088 |

Receive length field mismatch register offset.

Definition at line 242 of file at91_emac.h.

| #define EMAC_RLE (EMAC_BASE + EMAC_RLE_OFF) |

Receive length field mismatch register address.

Definition at line 243 of file at91_emac.h.

| #define EMAC_TPF_OFF 0x0000008C |

Transmitted pause frames register offset.

Definition at line 244 of file at91_emac.h.

| #define EMAC_TPF (EMAC_BASE + EMAC_TPF_OFF) |

Transmitted pause frames register address.

Definition at line 245 of file at91_emac.h.

| #define EMAC_HRB_OFF 0x00000090 |

Hash address bottom[31:0].

Definition at line 250 of file at91_emac.h.

| #define EMAC_HRB (EMAC_BASE + EMAC_HRB_OFF) |

Hash address bottom[31:0].

Definition at line 251 of file at91_emac.h.

| #define EMAC_HRT_OFF 0x00000094 |

Hash address top[63:32].

Definition at line 252 of file at91_emac.h.

| #define EMAC_HRT (EMAC_BASE + EMAC_HRT_OFF) |

Hash address top[63:32].

Definition at line 253 of file at91_emac.h.

| #define EMAC_SA1L_OFF 0x00000098 |

Specific address 1 bottom, first 4 bytes.

Definition at line 254 of file at91_emac.h.

| #define EMAC_SA1L (EMAC_BASE + EMAC_SA1L_OFF) |

Specific address 1 bottom, first 4 bytes.

Definition at line 255 of file at91_emac.h.

| #define EMAC_SA1H_OFF 0x0000009C |

Specific address 1 top, last 2 bytes.

Definition at line 256 of file at91_emac.h.

| #define EMAC_SA1H (EMAC_BASE + EMAC_SA1H_OFF) |

Specific address 1 top, last 2 bytes.

Definition at line 257 of file at91_emac.h.

| #define EMAC_SA2L_OFF 0x000000A0 |

Specific address 2 bottom, first 4 bytes.

Definition at line 258 of file at91_emac.h.

| #define EMAC_SA2L (EMAC_BASE + EMAC_SA2L_OFF) |

Specific address 2 bottom, first 4 bytes.

Definition at line 259 of file at91_emac.h.

| #define EMAC_SA2H_OFF 0x000000A4 |

Specific address 2 top, last 2 bytes.

Definition at line 260 of file at91_emac.h.

| #define EMAC_SA2H (EMAC_BASE + EMAC_SA2H_OFF) |

Specific address 2 top, last 2 bytes.

Definition at line 261 of file at91_emac.h.

| #define EMAC_SA3L_OFF 0x000000A8 |

Specific address 3 bottom, first 4 bytes.

Definition at line 262 of file at91_emac.h.

| #define EMAC_SA3L (EMAC_BASE + EMAC_SA3L_OFF) |

Specific address 3 bottom, first 4 bytes.

Definition at line 263 of file at91_emac.h.

| #define EMAC_SA3H_OFF 0x000000AC |

Specific address 3 top, last 2 bytes.

Definition at line 264 of file at91_emac.h.

| #define EMAC_SA3H (EMAC_BASE + EMAC_SA3H_OFF) |

Specific address 3 top, last 2 bytes.

Definition at line 265 of file at91_emac.h.

| #define EMAC_SA4L_OFF 0x000000B0 |

Specific address 4 bottom, first 4 bytes.

Definition at line 266 of file at91_emac.h.

| #define EMAC_SA4L (EMAC_BASE + EMAC_SA4L_OFF) |

Specific address 4 bottom, first 4 bytes.

Definition at line 267 of file at91_emac.h.

| #define EMAC_SA4H_OFF 0x000000B4 |

Specific address 4 top, last 2 bytes.

Definition at line 268 of file at91_emac.h.

| #define EMAC_SA4H (EMAC_BASE + EMAC_SA4H_OFF) |

Specific address 4 top, last 2 bytes.

Definition at line 269 of file at91_emac.h.

| #define EMAC_TID_OFF 0x000000B8 |

Type ID checking register offset.

Definition at line 274 of file at91_emac.h.

| #define EMAC_TID (EMAC_BASE + EMAC_TID_OFF) |

Type ID checking register address.

Definition at line 275 of file at91_emac.h.

| #define EMAC_TPQ_OFF 0x000000BC |

Transmit pause quantum register offset.

Definition at line 276 of file at91_emac.h.

| #define EMAC_TPQ (EMAC_BASE + EMAC_TPQ_OFF) |

Transmit pause quantum register address.

Definition at line 277 of file at91_emac.h.

| #define EMAC_USRIO_OFF 0x000000C0 |

User input/output register offset.

Definition at line 282 of file at91_emac.h.

| #define EMAC_USRIO (EMAC_BASE + EMAC_USRIO_OFF) |

User input/output register address.

Definition at line 283 of file at91_emac.h.

| #define EMAC_RMII 0x00000001 |

Enable reduced MII.

Definition at line 285 of file at91_emac.h.

| #define EMAC_CLKEN 0x00000002 |

Enable tranceiver input clock.

Definition at line 286 of file at91_emac.h.

| #define EMAC_WOL_OFF 0x000000C4 |

Wake On LAN register offset.

Definition at line 291 of file at91_emac.h.

| #define EMAC_WOL (EMAC_BASE + EMAC_WOL_OFF) |

Wake On LAN register address.

Definition at line 292 of file at91_emac.h.

| #define EMAC_IP 0x0000FFFF |

ARP request IP address mask.

Definition at line 293 of file at91_emac.h.

| #define EMAC_MAG 0x00010000 |

Magic packet event enable.

Definition at line 294 of file at91_emac.h.

| #define EMAC_ARP 0x00020000 |

ARP request event enable.

Definition at line 295 of file at91_emac.h.

| #define EMAC_SA1 0x00040000 |

Specific address register 1 event enable.

Definition at line 296 of file at91_emac.h.

| #define EMAC_REV_OFF 0x000000FC |

Revision register offset.

Definition at line 301 of file at91_emac.h.

| #define EMAC_REV (EMAC_BASE + EMAC_REV_OFF) |

Revision register address.

Definition at line 302 of file at91_emac.h.

| #define EMAC_REVREF 0x0000FFFF |

Revision.

Definition at line 303 of file at91_emac.h.

| #define EMAC_PARTREF 0xFFFF0000 |

Part.

Definition at line 304 of file at91_emac.h.

| void EmacRxThread | ( | void * | arg | ) |

NIC receiver thread.

Definition at line 787 of file at91_emac.c.

References _NUTDEVICE::dev_dcb, _NUTDEVICE::dev_icb, EMAC_IER, EMAC_LINK_LOOPS, EMAC_RCOMP, EMAC_ROVR, EMAC_RXUBR, EMAC_TUND, ETHER_IS_UNICAST, ifnet::if_mac, ifnet::if_recv, _NETBUF::nb_dl, _EMACINFO::ni_insane, _EMACINFO::ni_mutex, _EMACINFO::ni_rx_rdy, _EMACINFO::ni_tx_quelen, _EMACINFO::ni_tx_queued, NutEventPost(), NutEventWait(), NutIrqEnable(), NutNetBufFree(), NutSleep(), NutThreadSetPriority(), outr, sig_EMAC, and _NBDATA::sz.

Referenced by EmacInit().

Send Ethernet packet.

| dev | Identifies the device to use. |

| nb | Network buffer structure containing the packet to be sent. The structure must have been allocated by a previous call NutNetBufAlloc(). |

Definition at line 875 of file at91_emac.c.

References _NUTDEVICE::dev_dcb, EMAC_COMP, EMAC_TSR, EMAC_UND, inr, _EMACINFO::ni_insane, _EMACINFO::ni_mutex, _EMACINFO::ni_tx_rdy, NutEventPost(), NutEventWait(), outr, _BufDescriptor::stat, and TXS_USED.

| int EmacInit | ( | NUTDEVICE * | dev | ) |

Initialize Ethernet hardware.

Applications should do not directly call this function. It is automatically executed during during device registration by NutRegisterDevice().

| dev | Identifies the device to initialize. |

Definition at line 943 of file at91_emac.c.

References _NUTDEVICE::dev_dcb, EMAC_LINK_LOOPS, EmacRxThread(), memset(), NUT_THREAD_NICRXSTACK, NUT_THREAD_STACK_ADD, NUT_THREAD_STACK_MULT, NutRegisterIrqHandler(), NutThreadCreate(), and sig_EMAC.

{

0,

{'e', 't', 'h', '0', 0, 0, 0, 0, 0},

IFTYP_NET,

0,

0,

&ifn_eth0,

&dcb_eth0,

EmacInit,

0,

0,

0,

0,

0,

0,

0

}

Device information structure.

A pointer to this structure must be passed to NutRegisterDevice() to bind this Ethernet device driver to the Nut/OS kernel. An application may then call NutNetIfConfig() with the name eth0 of this driver to initialize the network interface.

Definition at line 1002 of file at91_emac.c.

{

0,

{'e', 't', 'h', '0', 0, 0, 0, 0, 0},

IFTYP_NET,

AVR32_MACB_ADDRESS,

0,

&ifn_eth0,

&dcb_eth0,

EmacInit,

0,

0,

0,

0,

0,

0,

0

}

Device information structure.

A pointer to this structure must be passed to NutRegisterDevice() to bind this Ethernet device driver to the Nut/OS kernel. An application may then call NutNetIfConfig() with the name eth0 of this driver to initialize the network interface.