Ethernut Expansion Port

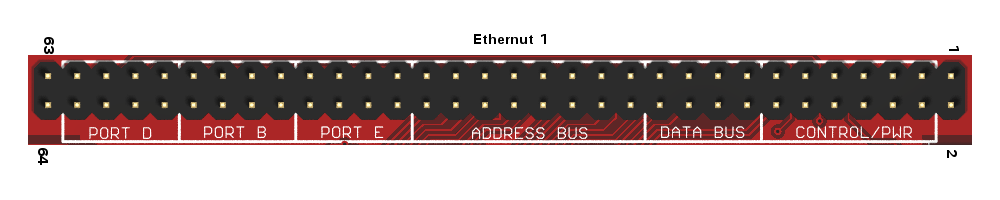

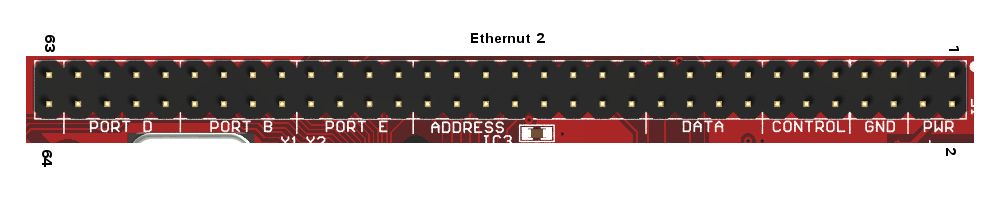

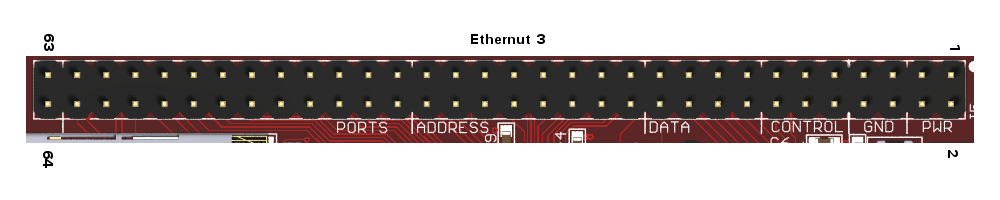

All Ethernut hardware reference designs share the same expansion port, a 64-pin header with two rows and 0.05" (2.54 mm) grid.

The connector layout had been originally specified for the 8-bit AVR on Ethernut 1 and 2. To maintain some compatibility, the port pins on ARM-based Ethernut 3 and 5 are not sorted in a specific order, but follow the AVR functions. This allows to develop add-on boards with, for example, I2C or SPI interfaces to be located at the same pins.

Important note: While all pins on Ethernut 1 are 5V CMOS compatible, and all pins on Ethernut 2 are at least 5V tolerant, some pins on Ethernut 3 and all pins on Ethernut 5 are 3.3V only. Applying voltages above 3.3V to these pins may destroy the board.

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

|---|---|---|---|

| 1 | VCC3 +3V Power Supply | VCC3 +3V Power Supply | VCC3 +3V Power Supply |

| 2 | VCC3 +3V Power Supply | VCC3 +3V Power Supply | VCC3 +3V Power Supply |

| 3 | VCC5 +5V Power Supply | N/C Not Connected | VCC5 +5V Power Supply |

| 4 | VCC5 +5V Power Supply | N/C Not Connected | VCC5 +5V Power Supply |

| 5 | GND Digital Ground | GND Digital Ground | GND Digital Ground |

| 6 | GND Digital Ground | GND Digital Ground | GND Digital Ground |

| 7 | GND Digital Ground | GND Digital Ground | GND Digital Ground |

| 8 | GND Digital Ground | GND Digital Ground | GND Digital Ground |

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

| 9 | NMR Hardware Reset I/O | NMR Hardware Reset Input | MR\ Hardware Reset Input |

| 10 | DC Unreg. Auxiliary Power Supply | DC Unreg. DC Power Supply | DC Unregulated DC Power Supply |

| 11 | VCC5 +5V Power Supply | N/C Not Connected | VCC5 +5V Power Supply |

| 12 | VCC5 +5V Power Supply | N/C Not Connected | VCC5 +5V Power Supply |

| 13 |

NRD Read Strobe CFOE CompactFlash Output Enable |

NCRD Configurable Read Strobe | RD\ External Memory Bus Read Strobe |

| 14 |

NWR0 Write Strobe NWE Write Enable |

NCWR Configurable Write Strobe | WR\ External Memory Bus Write Strobe |

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

| 15 | D0 External Data Bus Bit 0 | CDR0 Configurable Data Bus Bit 0 | D0 External Data Bus Bit 0 |

| 16 | D1 External Data Bus Bit 1 | CDR1 Configurable Data Bus Bit 1 | D1 External Data Bus Bit 1 |

| 17 | D2 External Data Bus Bit 2 | CDR2 Configurable Data Bus Bit 2 | D2 External Data Bus Bit 2 |

| 18 | D3 External Data Bus Bit 3 | CDR3 Configurable Data Bus Bit 3 | D3 External Data Bus Bit 3 |

| 19 | D4 External Data Bus Bit 4 | CDR4 Configurable Data Bus Bit 4 | D4 External Data Bus Bit 4 |

| 20 | D5 External Data Bus Bit 5 | CDR5 Configurable Data Bus Bit 5 | D5 External Data Bus Bit 5 |

| 21 | D6 External Data Bus Bit 6 | CDR6 Configurable Data Bus Bit 6 | D6 External Data Bus Bit 6 |

| 22 | D7 External Data Bus Bit 7 | CDR7 Configurable Data Bus Bit 7 | D7 External Data Bus Bit 7 |

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

| 23 |

A0 External Address Bus Bit 0 NBS0 Byte 0 Select |

CAR0 Configurable Address Bus Bit 0 |

A0 External Address Bus Bit 0 PA0 GPIO Port A Bit 0 |

| 24 |

A1 External Address Bus Bit 1 |

CAR1 Configurable Address Bus Bit 1 |

A1 External Address Bus Bit 1 PA1 GPIO Port A Bit 1 |

| 25 |

A2 External Address Bus Bit 2 |

CAR2 Configurable Address Bus Bit 2 |

A2 External Address Bus Bit 2 PA2 GPIO Port A Bit 2 |

| 26 |

A3 External Address Bus Bit 3 |

CAR3 Configurable Address Bus Bit 3 |

A3 External Address Bus Bit 3 PA3 GPIO Port A Bit 3 |

| 27 |

A4 External Address Bus Bit 4 |

CAR4 Configurable Address Bus Bit 4 |

A4 External Address Bus Bit 4 PA4 GPIO Port A Bit 4 |

| 28 |

A5 External Address Bus Bit 5 |

CAR5 Configurable Address Bus Bit 5 |

A5 External Address Bus Bit 5 PA5 GPIO Port A Bit 5 |

| 29 |

A6 External Address Bus Bit 6 |

CAR6 Configurable Address Bus Bit 6 |

A6 External Address Bus Bit 6 PA6 GPIO Port A Bit 6 |

| 30 |

A7 External Address Bus Bit 7 |

CAR7 Configurable Address Bus Bit 7 |

A7 External Address Bus Bit 7 PA7 GPIO Port A Bit 7 |

| 31 |

A8 External Address Bus Bit 8 |

CAR8 Configurable Address Bus Bit 8 |

A8 External Address Bus Bit 8 PC0 GPIO Port C Bit 0 |

| 32 |

A9 External Address Bus Bit 9 |

CAR9 Configurable Address Bus Bit 9 |

A9 External Address Bus Bit 9 PC1 GPIO Port C Bit 1 |

| 33 |

A10 External Address Bus Bit 10 |

CAR10 Configurable Address Bus Bit 10 |

A10 External Address Bus Bit 10 PC2 GPIO Port C Bit 2 |

| 34 |

A11 External Address Bus Bit 11 |

CAR11 Configurable Address Bus Bit 11 |

A11 External Address Bus Bit 11 PC3 GPIO Port C Bit 3 |

| 35 |

A12 External Address Bus Bit 12 |

CAR12 Configurable Address Bus Bit 12 |

A12 External Address Bus Bit 12 PC4 GPIO Port C Bit 4 |

| 36 |

A13 External Address Bus Bit 13 |

CAR13 Configurable Address Bus Bit 13 |

A13 External Address Bus Bit 13 PC5 GPIO Port C Bit 5 |

| 37 |

A14 External Address Bus Bit 14 |

CAR14 Configurable Address Bus Bit 14 |

A14 External Address Bus Bit 14 PC6 GPIO Port C Bit 6 |

| 38 |

A15 External Address Bus Bit 15 |

CAR15 Configurable Address Bus Bit 15 |

A15 External Address Bus Bit 15 PC7 GPIO Port C Bit 7 |

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

| 39 |

PC1 GPIO Port C Bit 1 PCK0 PLL Clock Output 0 ADC1 Analog Input Channel 1 |

P15 GPIO Port Bit 15 RXD0 UART 0 Receive Input |

PE0 GPIO Port E Bit 0 RXD0 UART 0 Receive Input PDI Programming Data Input |

| 40 |

PC0 GPIO Port C Bit 0 SCK3 UART 3 External Clock ADC0 Analog Input Channel 0 |

P14 GPIO Port Bit 14 TXD0 UART 0 Transmit Output |

PE1 GPIO Port E Bit 1 TXD0 UART 0 Transmit Output PDO Programming Data Output |

| 41 |

PC5 GPIO Port C Bit 5 A24 External Address Bus Bit 24 SPI1_NPCS1 SPI 1 Peripheral Chip Select 1 |

P13 GPIO Port Bit 13 SCK0 USART 0 External Clock |

PE2 GPIO Port E Bit 2 XCK0 USART 0 External Clock AIN0 Analog Comparator Positive Input |

| 42 |

PC4 GPIO Port C Bit 4 A23 External Address Bus Bit 23 SPI1_NPCS2 SPI 1 Peripheral Chip Select 2 |

P8 GPIO Port Bit 8 TIOB2 Counter Channel 2 I/O Line B |

PE3 GPIO Port E Bit 3 OC3A Counter 3 Compare and PWM A AIN1 Analog Comparator Positive Input |

| 43 |

PC7 GPIO Port C Bit 7 TIOB1 Counter Channel 1 I/O Line B CFCE2 CompactFlash Chip Enable 2 |

P9 GPIO Port Bit 9 IRQ0 External Interrupt Request 1 |

PE4 GPIO Port E Bit 4 INT4 External Interrupt 4 OC3B Counter 3 Compare and PWM B |

| 44 |

PC6 GPIO Port C Bit 6 TIOB2 Counter Channel 2 I/O Line B CFCE1 CompactFlash Chip Enable 1 |

P27 GPIO Port Bit 27 NCS3 Chip Select Line 3 |

PE5 GPIO Port E Bit 5 INT5 External Interrupt 5 OC3C Counter 3 Compare and PWM C |

| 45 |

PC15 GPIO Port C Bit 15 NWAIT Memory Bus Wait IRQ1 External Interrupt Request 1 |

P11 GPIO Port Bit 11 IRQ2 External Interrupt Request 2 |

PE6 GPIO Port E Bit 6 INT6 External Interrupt 6 T3 Counter 3 Clock Input |

| 46 |

PC13 GPIO Port C Bit 13 FIQ Fast Interrupt Request NCS6 Chip Select Line 6 |

P12 GPIO Port Bit 12 FIQ Fast Interrupt Request |

PE7 GPIO Port E Bit 7 INT7 External Interrupt 7 ICP3 Counter 3 Input Capture |

| 47 |

PB3 GPIO Port B Bit 3 SPI1_NPCS0 SPI 1 Peripheral Chip Select 0 TIOA5 Counter Channel 5 I/O Line A |

P0 GPIO Port Bit 0 TCLK0 External Clock Counter Channel 0 |

PB0 GPIO Port B Bit 0 -SS SPI Slave Select Input |

| 48 |

PB2 GPIO Port B Bit 2 SPI1_SPCK SPI 1 Serial Clock TIOA4 Counter Channel 4 I/O Line A |

P1 GPIO Port Bit 1 TIOA0 Counter Channel 0 I/O Line A |

PB1 GPIO Port B Bit 1 SCK SPI Bus Serial Clock |

| 49 |

PB1 GPIO Port B Bit 1 SPI1_MOSI SPI Bus Master Output / Slave Input TIOB3 Counter Channel 3 I/O Line B |

P2 GPIO Port Bit 2 TIOB0 Counter Channel 0 I/O Line B |

PB2 GPIO Port B Bit 2 MOSI SPI Bus Master Output / Slave Input |

| 50 |

PB0 GPIO Port B Bit 0 SPI1_MISO SPI Bus Master Input / Slave Output TIOA3 Counter Channel 3 I/O Line A |

P3 GPIO Port Bit 3 TCLK1 External Clock Counter Channel 0 |

PB3 GPIO Port B Bit 3 MISO SPI Bus Master Input / Slave Output |

| 51 |

PB17 GPIO Port B Bit 17 TF0 SSC Transmit Frame Sync TCLK4 External Clock Input Counter Channel 4 |

P4 GPIO Port Bit 4 TIOA1 Counter Channel 1 I/O Line A |

PB4 GPIO Port B Bit 4 OC0 Counter 0 Compare and PWM |

| 52 |

PB16 GPIO Port B Bit 16 TK0 SSC Transmit Clock TCLK3 External Clock Input Counter Channel 3 |

P5 GPIO Port Bit 5 TIOB1 Counter Channel 1 I/O Line B |

PB5 GPIO Port B Bit 5 OC1A Counter 1 Compare and PWM A |

| 53 |

PB19 GPIO Port B Bit 19 RD0 SSC Receive Data TIOB5 Counter Channel 5 I/O Line B |

P6 GPIO Port Bit 6 TCLK2 External Clock Counter Channel 0 |

PB6 GPIO Port B Bit 6 OC1B Counter 1 Compare and PWM B |

| 54 |

PB18 GPIO Port B Bit 18 TD0 SSC Transmit Data TIOB4 Counter Channel 4 I/O Line B |

P7 GPIO Port Bit 7 TIOA2 Counter Channel 2 I/O Pin A |

PB7 GPIO Port B Bit 7 OC1C Counter 1 Compare and PWM C OC2 Counter 2 Compare and PWM |

| Pin | Ethernut 5 (ARM9) | Ethernut 3 (ARM7) | Ethernut 1/2 (AVR) |

| 55 |

PA24 GPIO Port A Bit 24 TWCK0 TWI Serial Clock ETX3 MII Transmit Data Bit 3 |

P17 GPIO Port Bit 17 |

PD0 GPIO Port D Bit 0 INT0 External Interrupt 0 SCL TWI Serial Clock |

| 56 |

PA23 GPIO Port A Bit 23 TWD TWI Serial Data ETX2 MII Transmit Data Bit 2 |

P16 GPIO Port Bit 16 |

PD1 GPIO Port D Bit 1 INT1 External Interrupt 1 SDA TWI Serial Data |

| 57 |

PA26 GPIO Port A Bit 26 TIOA0 Counter Channel 0 I/O Line A TCLK2 External Clock Input Counter Channel 2 |

P22 GPIO Port Bit 22 RXD1 UART 1 Receive Input |

PD2 GPIO Port D Bit 2 INT2 External Interrupt 2 RXD1 UART 1 Receive Input |

| 58 |

PA25 GPIO Port A Bit 25 TCLK0 External Clock Input Counter Channel 0 ERX2 MII Receive Data Bit 2 |

P21 GPIO Port Bit 21 TXD1 UART 1 Transmit Output NTRI Three-State Mode Select |

PD3 GPIO Port D Bit 3 INT3 External Interrupt 3 TXD1 UART 1 Transmit Output |

| 59 |

PA28 GPIO Port A Bit 28 TIOA2 Counter Channel 2 I/O Line A ECRS MII Carrier Sense and Data Valid |

P23 GPIO Port Bit 23 |

PD4 GPIO Port D Bit 4 ICP1 Counter 1 Input Capture |

| 60 |

PA27 GPIO Port A Bit 27 TIOA1 Counter Channel 1 I/O Line A ERXCK MII Receive Clock |

P20 GPIO Port Bit 20 SCK1 USART 1 External Clock |

PD5 GPIO Port D Bit 5 XCK1 USART 1 External Clock |

| 61 |

PA29 GPIO Port A Bit 29 SCK1 USART 1 Serial Clock ECOL MII Collision Detect |

P19 GPIO Port Bit 19 |

PD6 GPIO Port D Bit 6 T1 Counter 1 Clock Input |

| 62 |

PA22 GPIO Port A Bit 22 ADTRG ADC Trigger ETXER MII Transmit Coding Error |

P18 GPIO Port Bit 18 |

PD7 GPIO Port D Bit 7 T2 Counter 2 Clock Input |

| 63 | N/C Not Connected | N/C Not Connected | N/C Not Connected |

| 64 | N/C Not Connected | N/C Not Connected |

N/C if R34 not mounted ALE External Address Bus Latch Enable |