Ethernut 5 JTAG

Auf Ethernut 5 befindet sich ein 20-poliger Steckverbinder (J7) zum Anschluss von JTAG Adaptern. Er befindet sich direkt hinter dem Sockel für die Speicherkarte.

Zusätzlich gibt es einen Jumper (JP2, seitlich am Speicherkartensockel), mit dem man den JTAG Boundary Scan aktivieren (Pin 3 mit Pin 4 verbinden) ...

... und den Flashspeicher der CPU löschen kann (Pin 1 mit Pin 2 verbinden).

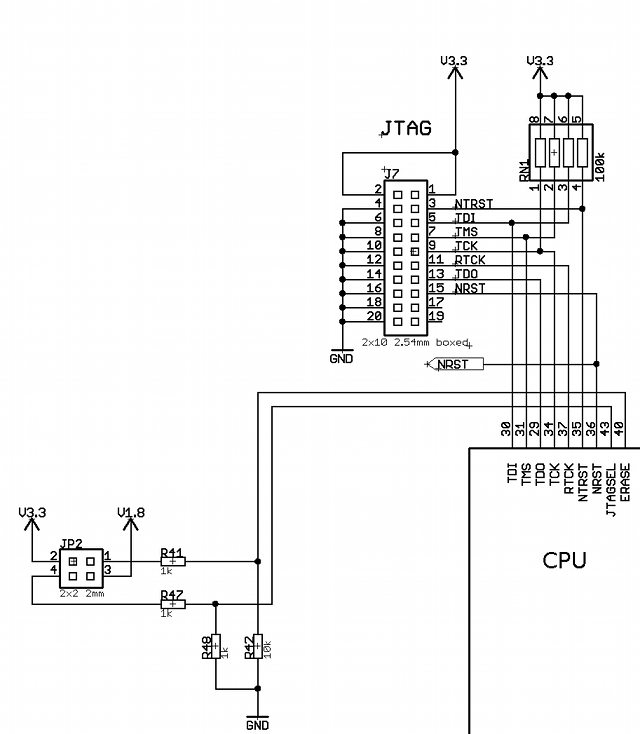

Die folgende Abbildung zeigt den relevanten Ausschnitt aus dem Schaltplan:

Man beachte, dass die Steckkontakte direkt mit den Pins der CPU verbunden sind. Man muss beim Stecken oder Entfernen des JTAG Adapters entsprechend vorsichtig vorgehen, um elektrostatische Entladungen am Steckverbinder zu vermeiden. In jedem Fall muss das Board vorher von der Versorgungsspannung getrennt werden.

Steckerbelegung

Die Belegung entspricht dem Industriestandard für ARM Boards.

| Ethernut 5 JTAG Connector Layout | |

|---|---|

| Voltage Reference Output VTref - 1 | 2 - Vsupply Adapter Supply Output |

| TAP Controller Reset Input nTRST - 3 | 4 - GND |

| Data Input TDI - 5 | 6 - GND |

| Test Mode Select Input TMS - 7 | 8 - GND |

| Clock Input TCK - 9 | 10 - GND |

| Return Clock output RTCK - 11 | 12 - GND |

| Data Output TDO - 13 | 14 - GND |

| Board Reset nSRST - 15 | 16 - GND |

| N/C - 17 | 18 - GND |

| N/C - 19 | 20 - GND |

Anschluss Turtelizer 2

Zum Anschluss des 10-poligen JTAG-Steckers von Turtelizer 2 an den 20-poligen Stecker von Ethernut 5 ist ein Adapter erforderlich.

OpenOCD für Ethernut 5 anpassen

Während der Entwicklungs- und Testphase bietet es sich an, die Firmware direkt ins externe SDRAM zu laden und dort auszuführen. Dazu benötigt man das Programm OpenOCD. Eine unter Windows lauffähige Version gibt es von Freddy Chopin.

Der Hersteller des Turtelizers, die egnite GmbH, bietet ebenfalls eine Version für Windows mit den dazugehörigen USB-Treibern auf seiner Produktseite an (auf Ressourcen klicken).

Nach der Installation des Pakets und der ggf. notwendigen USB Treiber sollte man die folgenden Konfigurationsdateien in das Installationsverzeichnis von OpenOCD übertragen oder zumindest mit den eventuell bereits installierten Dateien vergleichen. Es handelt sich dabei um einfache Textdateien, die man auch per Editor (Notepad o.ä.) von dieser Webseite übernehmen kann. Getestet wurden diese Dateien mit OpenOCD Version 0.6.1.

-

board/ethernut5.cfg

Konfigurationsdatei für Ethernut 5. Diese ist bisher noch nicht Bestandteil des offiziellen OpenOCD-Pakets. -

interface/turtelizer2.cfg

Konfigurationsdatei speziell für Turtelizer 2, welche üblicherweise bereits vorhanden sein sollte. Bei Verwendung anderer JTAG Adpater ist statt dessen die dafür passende Konfiguration notwendig. -

target/at91sam9260.cfg

target/at91sam9.cfg

Allgemeine Konfigurationen für die AT91SAM9260 CPU, die der AT91SAM9XE CPU auf Ethernut 5 entspricht. Diese Dateien sind Bestandteil von OpenOCD, werden hier aber zum Vergleich aufgelistet.

Eine ausführlichere Beschreibung der Konfiguration finden Sie auf der Seite OpenOCD Configuration for Ethernut 5 in englischer Sprache.

Die erste Datei ethernut5.cfg gehört in das Unterverzeichnis board und ist die umfangreichste:

# We add to the minimal configuration.

source [find target/at91sam9260.cfg]

# If DCC downloads are enabled, we need a work area.

# The configuration line below is intentionally commented,

# because this option may fail when code is directly loaded

# into internal SRAM. In this case you may provide another

# area, a few kB will do. The configuration below will occupy

# the complete SRAM.

#$_TARGETNAME configure -work-area-phys 0x00300000 -work-area-size 0x8000

$_TARGETNAME configure -event reset-start {

# At reset CPU runs at 32.768 kHz.

# JTAG Frequency must be 6 times slower if RCLK is not supported.

jtag_rclk 5

# For memory access we must halt the CPU

halt

wait_halt

# Optionally enable DCC downloads. If enabled,

# a work area must be provided too (see above).

arm7_9 dcc_downloads enable ;# Enable faster DCC downloads

# RSTC_MR : enable user reset, MMU may be enabled... use physical address

mww phys 0xfffffd08 0xa5000501

}

$_TARGETNAME configure -event reset-init {

mww 0xfffffd44 0x00008000 ;# WDT_MR : disable watchdog

mww 0xfffffc20 0x00004001 ;# CKGR_MOR : enable the main oscillator

sleep 20 ;# wait 20 ms

mww 0xfffffc30 0x00000001 ;# PMC_MCKR : switch to main oscillator

sleep 10 ;# wait 10 ms

mww 0xfffffc28 0x2060bf09 ;# CKGR_PLLAR: Set PLLA Register for 198.656 MHz

sleep 20 ;# wait 20 ms

mww 0xfffffc30 0x00000101 ;# PMC_MCKR : Select prescaler (divide by 2)

sleep 10 ;# wait 10 ms

mww 0xfffffc30 0x00000102 ;# PMC_MCKR : Clock from PLLA is selected (99.328 MHz)

sleep 10 ;# wait 10 ms

# Increase JTAG Speed to 6 MHz if RCLK is not supported

jtag_rclk 5000

# Fast memory access may fail, when the CPU is running

# in slow clock mode. Intentionally disabled by default.

arm7_9 fast_memory_access enable

mww 0xfffff870 0xffff0000 ;# PIO_ASR : Select peripheral function for D15..D31

mww 0xfffff804 0xffff0000 ;# PIO_PDR : Disable PIO function for D15..D31

mww 0xffffef1c 0x00010002 ;# EBI_CSA : Assign EBI Chip Select 1 to SDRAM, VDDIOMSEL set for +3V3 memory

mww 0xffffea08 0x85227259 ;# SDRAMC_CR : Configure SDRAM (2 x Micron MT48LC16M16A2 : 4M x 16Bit x 4 Banks)

mww 0xffffea00 0x1 ;# SDRAMC_MR : issue a NOP command

mww 0x20000000 0

mww 0xffffea00 0x2 ;# SDRAMC_MR : issue an 'All Banks Precharge' command

mww 0x20000000 0

mww 0xffffea00 0x4 ;# SDRAMC_MR : issue 8 x 'Auto-Refresh' Command

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x4

mww 0x20000000 0

mww 0xffffea00 0x3 ;# SDRAMC_MR : issue a 'Load Mode Register' command

mww 0x20000000 0

mww 0xffffea00 0x0 ;# SDRAMC_MR : normal mode

mww 0x20000000 0

mww 0xffffea04 0x2b6 ;# SDRAMC_TR : Set refresh timer count to 7us

# mww 0xFFFFEF00 0x00000003 ;# MATRIX_MRCR : Remap internal SRAM to address 0

}

Die Datei turtelizer2.cfg liegt im Unterverzeichnis interface und ist Bestandteil der offiziellen OpenOCD Quellen.

interface ft2232 ft2232_device_desc "Turtelizer JTAG/RS232 Adapter" ft2232_layout turtelizer2 ft2232_vid_pid 0x0403 0xbdc8 reset_config trst_and_srst

Bei Verwendung der OpenOCD Version von egnite ist der erste Eintrag gegen

interface turtle

auszutauschen.

Diese basiert auf den beiden Dateien at91sam9260.cfg und at91sam9.cfg im Unterverzeichnis target. Erstere sollte folgenden Inhalt haben:

if { [info exists CHIPNAME] } {

set AT91_CHIPNAME $CHIPNAME

} else {

set AT91_CHIPNAME at91sam9260

}

source [find target/at91sam9.cfg]

# Establish internal SRAM memory work areas that are important to pre-bootstrap loaders, etc. The

# AT91SAM9260 has two SRAM areas, one starting at 0x00200000 and the other starting at 0x00300000.

# Both areas are 4 kB long.

#$_TARGETNAME configure -work-area-phys 0x00200000 -work-area-size 0x1000 -work-area-backup 1

$_TARGETNAME configure -work-area-phys 0x00300000 -work-area-size 0x1000 -work-area-backup 1

Die Datei at91sam9.cfg hat den Inhalt:

######################################

# Target: Atmel AT91SAM9

######################################

if { [info exists AT91_CHIPNAME] } {

set _CHIPNAME $AT91_CHIPNAME

} else {

error "you must specify a chip name"

}

if { [info exists ENDIAN] } {

set _ENDIAN $ENDIAN

} else {

set _ENDIAN little

}

if { [info exists CPUTAPID] } {

set _CPUTAPID $CPUTAPID

} else {

set _CPUTAPID 0x0792603f

}

reset_config trst_and_srst separate trst_push_pull srst_open_drain

jtag newtap $_CHIPNAME cpu -irlen 4 -ircapture 0x1 -irmask 0xf -expected-id $_CPUTAPID

adapter_nsrst_delay 300

jtag_ntrst_delay 200

jtag_rclk 3

######################

# Target configuration

######################

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME arm926ejs -endian $_ENDIAN -chain-position $_TARGETNAME -variant arm926ejs

Nach erfolgreicher Installation und Anpassung der Konfiguration sollte man OpenOCD von der Kommandozeile aufrufen können.

openocd -v

Das Programm meldet sich mit seiner Versionsnummer und beendet sich dann wieder.

Open On-Chip Debugger 0.6.1 (2012-10-14-15:28)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.sourceforge.net/doc/doxygen/bugs.html

Bei Verwendung von Turtelizer 2 mit Ethernut 5 kann man mit folgendem Kommado die JTAG-Funktionalität testen. Denken Sie daran, dass man zum Anschließen des Adapters das Board von der Versorgung trennen muss.

openocd -s C:/ethernut/nut/tools/turtelizer2 \

-c "source [find interface/turtelizer2.cfg]" \

-c "source [find board/ethernut5.cfg]"

Windows Anwender geben alles in einer Zeile ein, ohne die beiden Backslashes am Ende. In der Regel muss auch der Suchpfad in der ersten Zeile entsprechend der Installation von OpenOCD auf Ihrem PC angepasst werden.

Wenn alles wie erwartet funktioniert, meldet sich OpenOCD in etwa mit

Open On-Chip Debugger 0.6.1 (2012-10-14-15:28)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.sourceforge.net/doc/doxygen/bugs.html

Info : only one transport option; autoselect 'jtag'

trst_and_srst separate srst_gates_jtag trst_push_pull srst_open_drain

trst_and_srst separate srst_gates_jtag trst_push_pull srst_open_drain

adapter_nsrst_delay: 300

jtag_ntrst_delay: 200

RCLK - adaptive

Info : device: 4 "2232C"

Info : deviceID: 67354056

Info : SerialNumber: TLVE8EUJA

Info : Description: Turtelizer JTAG/RS232 Adapter A

Info : RCLK (adaptive clock speed) not supported - fallback to 3 kHz

Info : JTAG tap: at91sam9260.cpu tap/device found: 0x0792603f (mfg: 0x01f, part: 0x7926, ver: 0x0)

Info : Embedded ICE version 6

Info : at91sam9260.cpu: hardware has 2 breakpoint/watchpoint units

Entscheidend ist die Zeile

JTAG tap: at91sam9260.cpu tap/device found: 0x0792603f

Hieraus lässt sich ablesen, dass OpenOCD eine Verbindung zum Board herstellen und deren ID auslesen konnte. Antwortet OpenOCD dagegen mit

Error: JTAG scan chain interrogation failed: all ones Error: Check JTAG interface, timings, target power, etc. Error: Trying to use configured scan chain anyway... Error: at91sam9260.cpu: IR capture error; saw 0x0f not 0x01

dann ist vermutlich die JTAG Verbindung unterbrochen oder die Spannungsversorgung von Ethernut 5 nicht eingeschaltet.

Erscheint statt dessen die Meldung

Error: unable to open ftdi device: device not found

und OpenOCD beendet sich sofort wieder, dann wurde der JTAG Adapter nicht erkannt. Bei USB-basierten Adaptern wie Turtelizer 2 hilft hier manchmal ein kurzzeitiges Trennen der USB Verbindung oder ein Neustart des Rechners.

Weitere Details werden ausführlich im OpenOCD Manual beschrieben. Zum Beenden des Programms drücken Sie Strg+C (Control+C).

Nut/OS Anwendungen ins SDRAM laden

Hat man OpenOCD erfolgreich konfiguriert, kann man mit folgendem Kommado ein binäres Firmware-Image auf das Board übertragen und dort starten:

openocd -s <Suchpfad> \

-c "source [find <Adapterkonfiguration>]" \

-c "source [find <Boardkonfiguration>]" \

-c init \

-c "reset init" \

-c "load_image <Imagedatei> 0x20000000" \

-c "verify_image <Imagedatei> 0x20000000" \

-c "resume 0x20000000"

-c shutdown

Dabei sind zu ersetzen

-

<Suchpfad>

mit dem Installationsverzeichnis von OpenOCD, z.B. C:/ethernut/nut/tools/turtelizer2. -

<Adapterkonfiguration>

mit der Konfigurationsdatei für den JTAG-Adapter, z.B. interface/turtelizer2.cfg. -

<Boardkonfiguration>

mit der Konfigurationsdatei für das Board, also board/ethernut5.cfg im Falle von Ethernut 5. -

<Imagedatei>

mit der Datei die das binäre Image enthält, z.B. caltime.bin.

Um z.B. das Programm zum Auslesen von Datum und Uhrzeit auf dem Ethernut 5 mit Hilfe des Turtelizer 2 zu starten, lautet der vollständige Befehl:

openocd -s ../../nut/tools/turtelizer2 -c "source [find interface/turtelizer2.cfg]" \ -c "source [find board/ethernut5.cfg]" -c init -c "reset init" \ -c "load_image en5rtc_read.bin 0x20000000" -c "verify_image en5rtc_read.bin 0x20000000" \ -c "resume 0x20000000" -c shutdown

Wie üblich, muss man unter Windows alles in einer Zeile eingeben, ohne die Backslashes am Ende.

Komfortabler funktioniert das mit dem make Befehl:

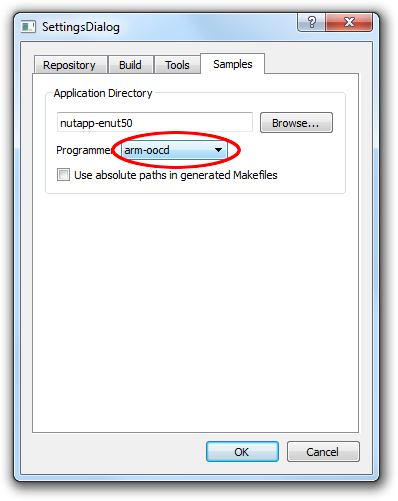

make burn

erstellt nicht nur die Firmware nach jeder Änderung, sondern startet sie anschließend automatisch auf dem Board. Damit das reibungslos funktioniert, muss man im Nut/OS Konfigurator auf der letzten Seite der Settings arm-oocd als Programmierer ausgewählt haben.

In der Datei nut/app/Makeburn.arm-oocd muss dann noch die Zeile

BURNDONGLE = turtelizer2

aktiviert sein (ohne führendes Nummernzeichen). Falls Sie eine ältere Version von Nut/OS als 5.1 verwenden, kann es sein, dass Ethernut 5 noch nicht berücksichtigt wurde. Sie können dies nachholen, indem Sie weiter unten (dort, wo die anderen Boards abgefragt werden), folgende Zeilen einfügen:

ifeq ($(PLATFORM), ETHERNUT5) BURNBOARD = ethernut5 # Initialize clocks and SDRAM. BURNCMDS += -c "reset init" ifeq ($(LDNAME), at91sam9xe512_ram) # Load image into external SDRAM. BURNCMDS += -c "load_image $(ITARG) 0x20000000" BURNCMDS += -c "verify_image $(ITARG) 0x20000000" BURNCMDS += -c "resume 0x20000000" endif # Programming AT91SAM9XE internal flash is not supported by OpenOCD. ifeq ($(LDNAME), at91sam9xe512_iram) # Load image into internal SRAM. BURNCMDS += -c "mww 0xFFFFEF00 0x00000003" BURNCMDS += -c "load_image $(ITARG) 0x00000000" BURNCMDS += -c "verify_image $(ITARG) 0x00000000" BURNCMDS += -c "resume 0x00000000" endif endif